**Instruction Manual**

# Tektronix

TMS 710 TMS320C6201/6701 Microprocessor Support 071-0202-01

Warning

The servicing instructions are for use by qualified personnel only. To avoid personal injury, do not perform any servicing unless you are qualified to do so. Refer to all safety summaries prior to performing service. Copyright © Tektronix, Inc. All rights reserved. Licensed software products are owned by Tektronix or its suppliers and are protected by United States copyright laws and international treaty provisions.

Use, duplication, or disclosure by the Government is subject to restrictions as set forth in subparagraph (c)(1)(ii) of the Rights in Technical Data and Computer Software clause at DFARS 252.227-7013, or subparagraphs (c)(1) and (2) of the Commercial Computer Software – Restricted Rights clause at FAR 52.227-19, as applicable.

Tektronix products are covered by U.S. and foreign patents, issued and pending. Information in this publication supercedes that in all previously published material. Specifications and price change privileges reserved.

Printed in the U.S.A.

Tektronix, Inc., P.O. Box 1000, Wilsonville, OR 97070-1000

TEKTRONIX and TEK are registered trademarks of Tektronix, Inc.

#### SOFTWARE WARRANTY

Tektronix warrants that the media on which this software product is furnished and the encoding of the programs on the media will be free from defects in materials and workmanship for a period of three (3) months from the date of shipment. If a medium or encoding proves defective during the warranty period, Tektronix will provide a replacement in exchange for the defective medium. Except as to the media on which this software product is furnished, this software product is provided "as is" without warranty of any kind, either express or implied. Tektronix does not warrant that the functions contained in this software product will meet Customer's requirements or that the operation of the programs will be uninterrupted or error-free.

In order to obtain service under this warranty, Customer must notify Tektronix of the defect before the expiration of the warranty period. If Tektronix is unable to provide a replacement that is free from defects in materials and workmanship within a reasonable time thereafter, Customer may terminate the license for this software product and return this software product and any associated materials for credit or refund.

THIS WARRANTY IS GIVEN BY TEKTRONIX IN LIEU OF ANY OTHER WARRANTIES, EXPRESS OR IMPLIED. TEKTRONIX AND ITS VENDORS DISCLAIM ANY IMPLIED WARRANTIES OF MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE. TEKTRONIX' RESPONSIBILITY TO REPLACE DEFECTIVE MEDIA OR REFUND CUSTOMER'S PAYMENT IS THE SOLE AND EXCLUSIVE REMEDY PROVIDED TO THE CUSTOMER FOR BREACH OF THIS WARRANTY. TEKTRONIX AND ITS VENDORS WILL NOT BE LIABLE FOR ANY INDIRECT, SPECIAL, INCIDENTAL, OR CONSEQUENTIAL DAMAGES IRRESPECTIVE OF WHETHER TEKTRONIX OR THE VENDOR HAS ADVANCE NOTICE OF THE POSSIBILITY OF SUCH DAMAGES.

### **Table of Contents**

|                         | General Safety Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                         | Service Safety Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                         | Preface      Manual Conventions      Contacting Tektronix                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Getting Started         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                         | Support Package DescriptionLogic Analyzer Software CompatibilityLogic Analyzer ConfigurationRequirements and RestrictionsFunctionality Not SupportedDAS Mass Termination Interface (MTIF) ProbesConnecting the Logic Analyzer to a System Under TestChannel AssignmentsCPU To Mictor Connections                                                                                                                                                                                            |

| <b>Operating Basics</b> |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                         | Setting Up the SupportChannel Group DefinitionsClockingSymbolsLogic Analyzer Time Alignment for the C6201Logic Analyzer Time Alignment for the C6701                                                                                                                                                                                                                                                                                                                                        |

|                         | Acquiring and Viewing Disassembled Data   2     Acquiring Data   2     Viewing Disassembled Data   2     Timing Display Format   2     State-Listing Display Format   2     Hardware Display Format   2     Software Display Format   2     Control Flow Display Format   2     Subroutine Display Format   2     Optional Display Selections   2     Micro Specific Fields   2     Marking Cycles   2     Displaying Exception Vectors   2     Viewing an Example of Disassembled Data   2 |

| Specifications          | - •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Replaceable Parts       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

Index

### List of Figures

| Figure 1–1: Pin assignments for a Mictor connector                |      |

|-------------------------------------------------------------------|------|

| (component side)                                                  | 1–11 |

| Figure 2–1: Bus timing for the ASYNC Memory Read operation        | 2–2  |

| Figure 2–2: Bus timing for the ASYNC Memory Write operation       | 2–3  |

| Figure 2–3: Bus timing for the SBSRAM Memory Read operation       | 2–4  |

| Figure 2–4: Bus timing for the SBSRAM Memory Write operation .    | 2–5  |

| Figure 2–5: Bus timing for the SDRAM Memory Read operation        | 2–6  |

| Figure 2–6: Bus timing for the SDRAM Memory Write operation       | 2–7  |

| Figure 2–7: Bus timing for the SDRAM row address activation cycle | 2–8  |

| Figure 2–8: C6201 Setup: Load System menu                         | 2–10 |

| Figure 2–9: C6201 Load System Options dialog box                  | 2–11 |

| Figure 2–10: C6201 System window with the C6201 Cal Setup file    | 2–12 |

| Figure 2–11: C6201 Custom options C6201 dialog box                | 2–13 |

| Figure 2–12: C6201 Trigger setup for any asynchronous memory      |      |

| Read                                                              | 2–13 |

| Figure 2–13: C6201 Asynchronous memory read timing diagram        | 2–14 |

| Figure 2–14: C6201 Trigger setup for any SBSRAM memory            |      |

| Read                                                              | 2–15 |

| Figure 2–15: C6201 SBSRAM memory read timing (full-rate SSCLK)    |      |

| diagram                                                           | 2–16 |

| Figure 2–16: C6201 Custom options C6201 dialog box                | 2–17 |

| Figure 2–17: C6701 Setup: Load System menu                        | 2–18 |

| Figure 2–18: C6701 Load System Options dialog box                 | 2–19 |

| Figure 2–19: C6701 System window with the Cal Setup file          | 2–20 |

| Figure 2–20: C6201 Custom options C6201 dialog box                | 2–20 |

| Figure 2–21: C6701 Custom options dialog box                      | 2–21 |

| Figure 2–22: C6701 Trigger setup for any asynchronous memory      |      |

| Read                                                              | 2–21 |

| Figure 2–23: C6701 Asynchronous memory read timing diagram        | 2–22 |

| Figure 2–24: C6701 Trigger setup for any SBSRAM memory Read .     | 2–23 |

| Figure 2–25: C6701 Custom options dialog box                      | 2–24 |

| Figure 2–25: Hardware display format                              | 2–27 |

### List of Tables

| Table 1–1: Module compatibility specifications                | 1–2  |

|---------------------------------------------------------------|------|

| Table 1–2: Address channel group assignments                  | 1–4  |

| Table 1–3: Data channel group assignments                     | 1–5  |

| Table 1–4: AsyncCtrl channel group assignments                | 1–6  |

| Table 1–5: SbsramCtrl channel group assignments               | 1–7  |

| Table 1–6: SdramCtrl channel group assignments                | 1–7  |

| Table 1–7: Control channel group assignments                  | 1–7  |

| Table 1–8: ByteEnbl channel group assignments                 | 1–8  |

| Table 1–9: CESpace channel group assignments                  | 1–8  |

| Table 1–10: Intr channel group assignments                    | 1–8  |

| Table 1–11: Misc channel group assignments                    | 1–9  |

| Table 1–12: Clock and Qualifier channel assignments           | 1–9  |

| Table 1–13: Signals not required for clocking and disassembly | 1–10 |

| Table 1–14: CPU to Mictor connections for Mictor A pins       | 1–11 |

| Table 1–15: CPU to Mictor connections for Mictor D pins       | 1–13 |

| Table 1–16: CPU to Mictor connections for Mictor C pins       | 1–14 |

| Table 2–1: Control group symbol table definitions             | 2–9  |

| Table 2–2: C6201 Memory types and maximum frequencies         | 2–10 |

| Table 2–3: C6201 Setup time for the AsyncCtrl group           | 2–15 |

| Table 2–4: C6201 Setup time for the SbsramCtrl group          | 2–16 |

| Table 2–5: C6701 Memory types and maximum frequencies         | 2–18 |

| Table 2–6: C6701 Setup time for the AsyncCtrl group           | 2–23 |

| Table 2–7: Description of special characters in the display   | 2–25 |

| Table 2–8: Cycle type definitions                             | 2–26 |

| Table 2–9: Exception vectors                                  | 2–31 |

| Table 3–1: C6201 Electrical specifications                    | 3–1  |

| Table 3–2: C6701 Electrical Specifications                    | 3–1  |

Table of Contents

### **General Safety Summary**

Review the following safety precautions to avoid injury and prevent damage to this product or any products connected to it. To avoid potential hazards, use this product only as specified.

Only qualified personnel should perform service procedures.

While using this product, you may need to access other parts of the system. Read the *General Safety Summary* in other system manuals for warnings and cautions related to operating the system.

**Connect and Disconnect Properly.** Do not connect or disconnect probes or test leads while they are connected to a voltage source.

**Ground the Product**. This product is indirectly grounded through the grounding conductor of the mainframe power cord. To avoid electric shock, the grounding conductor must be connected to earth ground. Before making connections to the input or output terminals of the product, ensure that the product is properly grounded.

**Observe All Terminal Ratings**. To avoid fire or shock hazard, observe all ratings and marking on the product. Consult the product manual for further ratings information before making connections to the product.

Do not apply a potential to any terminal, including the common terminal, that exceeds the maximum rating of that terminal.

**Do Not Operate Without Covers**. Do not operate this product with covers or panels removed.

**Avoid Exposed Circuitry.** Do not touch exposed connections and components when power is present.

**Do Not Operate With Suspected Failures.** If you suspect there is damage to this product, have it inspected by qualified service personnel.

Do Not Operate in Wet/Damp Conditions.

Do Not Operate in an Explosive Atmosphere.

Keep Product Surfaces Clean and Dry.

**Provide Proper Ventilation.** Refer to the manual's installation instructions for details on installing the product so it has proper ventilation.

Symbols and Terms in this Manual. These terms may appear in this manual:

**WARNING**. Warning statements identify conditions or practices that could result in injury or loss of life.

**CAUTION.** Caution statements identify conditions or practices that could result in damage to this product or other property.

Terms on the Product. These terms may appear on the product:

DANGER indicates an injury hazard immediately accessible as you read the marking.

WARNING indicates an injury hazard not immediately accessible as you read the marking.

CAUTION indicates a hazard to property including the product.

Symbols on the Product. The following symbols may appear on the product:

Protective Ground (Earth) Terminal

TMS 710 TMS320C6201/C6701 Microprocessor Support

# Service Safety Summary

Only qualified personnel should perform service procedures. Read this *Service Safety Summary* and the *General Safety Summary* before performing any service procedures.

**Do Not Service Alone**. Do not perform internal service or adjustments of this product unless another person capable of rendering first aid and resuscitation is present.

**Disconnect Power**. To avoid electric shock, disconnect the main power by means of the power cord or, if provided, the power switch.

**Use Care When Servicing With Power On**. Dangerous voltages or currents may exist in this product. Disconnect power, remove battery (if applicable), and disconnect test leads before removing protective panels, soldering, or replacing components.

To avoid electric shock, do not touch exposed connections.

### Preface

This instruction manual contains specific information about the TMS 710 TMS320C6201/C6701 microprocessor support package and is part of a set of information on how to operate this product on compatible Tektronix logic analyzers.

If you are familiar with operating microprocessor support packages on the logic analyzer for which the TMS 710 TMS320C6201/C6701 support was purchased, you will only need this instruction manual to set up and run the support.

If you are not familiar with operating microprocessor support packages, you will need to supplement this instruction manual with information on basic operations to set up and run the support. See Manual Conventions below for more information.

#### **Manual Conventions**

This manual uses the following conventions:

- The term "disassembler" refers to the software that disassembles bus cycles into instruction mnemonics and cycle types.

- The phrase "information on basic operations" refers to online help, an installation manual, or a user manual covering the basic operations of microprocessor support.

### Contacting Tektronix

| Product<br>Support    | For application-oriented questions about a Tektronix measure-<br>ment product, call toll free in North America:<br>1-800-TEK-WIDE (1-800-835-9433 ext. 2400)<br>6:00 a.m. – 5:00 p.m. Pacific time |

|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                       | Or, contact us by e-mail:<br>tm_app_supp@tek.com                                                                                                                                                   |

|                       | For product support outside of North America, contact your local Tektronix distributor or sales office.                                                                                            |

| Service<br>Support    | Contact your local Tektronix distributor or sales office. Or, visit our web site for a listing of worldwide service locations.                                                                     |

|                       | tektronix.com                                                                                                                                                                                      |

| For other information | In North America:<br>1-800-TEK-WIDE (1-800-835-9433)<br>An operator will direct your call.                                                                                                         |

| To write us           | Tektronix, Inc.<br>P.O. Box 1000<br>Wilsonville, OR 97070-1000                                                                                                                                     |

|                       |                                                                                                                                                                                                    |

# **Getting Started**

### **Getting Started**

This chapter contains information on the TMS 710 TMS320C6201/C6701 microprocessor support package, and information on connecting your logic analyzer to your system under test.

#### **Support Package Description**

The TMS 710 TMS320C6201/C6701microprocessor support package displays disassembled data from systems based on the Texas Instruments C6201/C6701 microprocessor.

To use this support efficiently, you need to have the items listed in the information on basic operations and the following documents:

- C62X/C67X CPU and Instruction SET Reference Guide, Texas Instruments, Feb 24 1998, PRU189C.

- C6201/C6701 Peripheral Reference Guide, Texas Instruments, March 1998, SPRU190A.

- C6701 Data sheet Texas Instruments, May 1998, SPRS067.

- C6201 Data sheet Texas Instruments, March 1998, SPRS051C.

Information on basic operations also contains a general description of support.

#### Logic Analyzer Software Compatibility

The floppy disk label on the microprocessor support states which version of logic analyzer software this support is compatible with.

#### Logic Analyzer Configuration

The TMS 710 TMS320C6201/C6701support requires a minimum of one 102-channel module.

The TMS 710 support will function with the Logic Analyzer acquisition modules. Table 1–1 lists the module compatibility specifications.

Table 1–1: Module compatibility specifications

| Characteristics                                           | Requirements |

|-----------------------------------------------------------|--------------|

| Tektronix Logic Analyzer                                  |              |

| Maximum bus speed                                         | 200 MHz      |

| Note:<br>CK0, CK1, CK2, and CK3 clock channels are stored |              |

#### **Requirements and Restrictions**

You should review the general requirements and restrictions of microprocessor support packages in the information on basic operations as they pertain to your system under test.

You should also review electrical, environmental, and mechanical specifications in *Specifications* on page 3–1 as they pertain to your system under test, as well as the following descriptions of other C6201/C6701 support requirements and restrictions.

**System Clock Rate** The operating speeds that the C6201/C6701 support can acquire data from the C6201/C6701 microprocessor are listed on Table 3–1. These specification were valid at the time this manual was printed. Please contact your Tektronix Sales Representative for current information on the fastest devices supported.

**Non Intrusive Acquisition** Acquiring microprocessor bus cycles will be non intrusive to the system under test. That is, the C6201/C6701 support will not intercept, modify, or present signals back to the system under test.

**Disabling the Instruction** Cache To display disassembled acquired data, you must disable the internal instruction cache. Disabling the cache makes all instruction prefetches visible on the bus they then can be acquired and displayed disassembled.

**Byte Invalidation** Invalid bytes cannot be dashed out during read cycles since byte enables are not asserted during read cycles.

**Opcode Fetch/Data Read.** The C6201/C6701 does not provide a signal to distinguish between Data Read and Opcode Fetch. The TMS 710 TMS320C6201/C6701 support makes a reasonable estimate at looking at the address values of a few sequences around the current sequence. Yet in some instances you may need to use the Mark Opcode function.

#### **Functionality Not Supported**

| Microprocessor       | The signals: DMA, HPI, MCBSP 0 & 1, and JTAG are not acquired. If you want to view these signals, you need to find an alternate way to probe them. |

|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| Alternate Bus master | Alternative bus master transactions are acquired by the C6201/C6701 support and are not disassembled.                                              |

### DAS Mass Termination Interface (MTIF) Probes

The MTIF probes are already labeled since the probe sections for each probe are permanent. The TMS 710 TMS320C6201/C6701 support channel assignments follow the standard channel mapping.

### Connecting the Logic Analyzer to a System Under Test

You can use channel probes, clock probes, and leadsets with a commercial test clip (or adapter) to make connections between the logic analyzer and your system under test.

To connect the probes to C6201/C6701 signals in the system under test using a test clip, follow these steps:

**1.** Turn off power to your system under test. It is not necessary to turn off power to the logic analyzer.

**CAUTION.** Static discharge can damage the microprocessor, the probes, and the logic analyzer module. To prevent static damage, handle these components only in a static-free environment.

Always wear a grounding wrist strap, heel strap, or similar device while handling the microprocessor.

**2.** To discharge your stored static electricity, touch the ground connector located on the back of the logic analyzer. If you are using a test clip, touch any of the ground pins on the clip to discharge stored static electricity from the test clip.

**CAUTION.** Failure to place the system under test on a horizontal surface before connecting the test clip can permanently damage the pins on the microprocessor.

- 3. Place the system under test on a horizontal static-free surface.

- **4.** Use Tables 1–2 through 1–10 to connect the channel probes to C6201/C6701 signal pins on the test clip or in the system under test.

Use leadsets to connect at least one ground lead from each channel probe and the ground lead from each clock probe to ground pins on your test clip.

#### **Channel Assignments**

Channel assignments listed in Tables 1–2 through 1–10 use the following conventions:

- All signals are required by the support unless indicated otherwise.

- Channels are listed starting with the most significant bit (MSB), descending to the least significant bit (LSB).

- Channel group assignments are for all modules unless otherwise noted.

- An asterisk symbol (\*) following a signal name indicates an active low signal.

- An equals symbol (=) following a signal name indicates that it is double probed.

Table 1–2 lists the probe section and channel assignments for the Address group and the microprocessor signal to which each channel connects. By default the Address channel group assignments are displayed in hexadecimal.

| Bit order | Section:channel | C6201/C6701 signal name |

|-----------|-----------------|-------------------------|

| 31        | A3:7            | GND                     |

| 30        | A3:6            | GND                     |

| 29        | A3:5            | GND                     |

| 28        | A3:4            | GND                     |

| 27        | A3:3            | GND                     |

| 26        | A3:2            | GND                     |

| 25        | A3:1            | GND                     |

| 24        | A3:0            | GND                     |

| 23        | A2:7            | GND                     |

Table 1–2: Address channel group assignments

| Bit order | Section:channel | C6201/C6701 signal name |

|-----------|-----------------|-------------------------|

| 22        | A2:6            | GND                     |

| 21        | A2:5            | EA21                    |

| 20        | A2:4            | EA20                    |

| 19        | A2:3            | EA19                    |

| 18        | A2:2            | EA18                    |

| 17        | A2:1            | EA17                    |

| 16        | A2:0            | EA16                    |

| 15        | A1:7            | EA15                    |

| 14        | A1:6            | EA14                    |

| 13        | A1:5            | EA13                    |

| 12        | A1:4            | EA12                    |

| 11        | A1:3            | EA11                    |

| 10        | A1:2            | EA10                    |

| 9         | A1:1            | EA9                     |

| 8         | A1:0            | EA8                     |

| 7         | A0:7            | EA7                     |

| 6         | A0:6            | EA6                     |

| 5         | A0:5            | EA5                     |

| 4         | A0:4            | EA4                     |

| 3         | A0:3            | EA3                     |

| 2         | A0:2            | EA2                     |

| 1         | A0:1            | GND                     |

| 0         | A0:0            | GND                     |

Table 1–2: Address channel group assignments (cont.)

Table 1–3 lists the probe section and channel assignments for the Data group and the microprocessor signal to which each channel connects. By default the Data channel group assignments are displayed in hexadecimal.

| Bit order | Section:channel | C6201/C6701 signal name |

|-----------|-----------------|-------------------------|

| 31        | D3:7            | ED31                    |

| 30        | D3:6            | ED30                    |

| 29        | D3:5            | ED29                    |

| 28        | D3:4            | ED28                    |

| 27        | D3:3            | ED27                    |

| 26        | D3:2            | ED26                    |

Table 1–3: Data channel group assignments

| Bit order | Section:channel | C6201/C6701 signal name |

|-----------|-----------------|-------------------------|

| 25        | D3:1            | ED25                    |

| 24        | D3:0            | ED24                    |

| 23        | D2:7            | ED23                    |

| 22        | D2:6            | ED22                    |

| 21        | D2:5            | ED21                    |

| 20        | D2:4            | ED20                    |

| 19        | D2:3            | ED19                    |

| 18        | D2:2            | ED18                    |

| 17        | D2:1            | ED17                    |

| 16        | D2:0            | ED16                    |

| 15        | D1:7            | ED15                    |

| 14        | D1:6            | ED14                    |

| 13        | D1:5            | ED13                    |

| 12        | D1:4            | ED12                    |

| 11        | D1:3            | ED11                    |

| 10        | D1:2            | ED10                    |

| 9         | D1:1            | ED9                     |

| 8         | D1:0            | ED8                     |

| 7         | D0:7            | ED7                     |

| 6         | D0:6            | ED6                     |

| 5         | D0:5            | ED5                     |

| 4         | D0:4            | ED4                     |

| 3         | D0:3            | ED3                     |

| 2         | D0:2            | ED2                     |

| 1         | D0:1            | ED1                     |

| 0         | D0:0            | ED0                     |

Table 1-3: Data channel group assignments (cont.)

Tables 1–4 through 1–6 appear only in the TLA 700 Series.

By default Table 1–4 AsyncCtrl channel group assignments are not displayed.

Table 1-4: AsyncCtrl channel group assignments

| Bit order | Section:channel | C6201/C6701 signal name |

|-----------|-----------------|-------------------------|

| 3         | C3:3            | ARE*                    |

| 2         | C3:5            | AWE *                   |

| Bit order | Section:channel | C6201/C6701 signal name |

|-----------|-----------------|-------------------------|

| 1         | CLK:0           | ARE* =                  |

| 0         | C2:3            | AWE*=                   |

Table 1–4: AsyncCtrl channel group assignments (cont.)

By default Table 1–5 SbsramCtrl channel group assignments are not displayed.

Table 1–5: SbsramCtrl channel group assignments

| Bit order | Section:channel | C6201/C6701 signal name |  |  |

|-----------|-----------------|-------------------------|--|--|

| 3         | C2:6            | SSADS*                  |  |  |

| 2         | C2:5            | SSOE*                   |  |  |

| 1         | C2:2            | SSWE*                   |  |  |

| 0         | Qual:0          | SSADS*=                 |  |  |

By default Table 1–6 SdramCtrl channel group assignments are not displayed.

Table 1–6: SdramCtrl channel group assignments

| Bit order | Section:channel | C6201/C6701 signal name |  |

|-----------|-----------------|-------------------------|--|

| 3         | C2:0            | SDRAS*                  |  |

| 2         | C2:1            | SDCAS*                  |  |

| 1         | C3:0            | SDWE*                   |  |

| 0         | Qual:1          | SDWE*=                  |  |

Table 1–7 lists the probe section and channel assignments for the Control group and the microprocessor signal to which each channel connects. The default radix of the Control group is SYMBOLIC on the TLA 700. The symbol table file name is C6201/C6701\_Ctrl on the TLA 700.

Table 1–7: Control channel group assignments

| Bit order | Section:channel | C6201/C6701 signal name |  |

|-----------|-----------------|-------------------------|--|

| 10        | C3:1            | RESET*                  |  |

| 9         | C3:2            | LENDIAN                 |  |

| 8         | C0:6            | HOLDA*                  |  |

| 7         | C2:0            | SDRAS*                  |  |

| 6         | C2:1            | SDCAS*                  |  |

| 5         | C3:0            | SDWE*                   |  |

| Bit order | Section:channel | C6201/C6701 signal name |  |

|-----------|-----------------|-------------------------|--|

| 4         | C2:6            | SSADS*                  |  |

| 3         | C2:5            | SSOE*                   |  |

| 2         | C2:2            | SSWE*                   |  |

| 1         | C3:3            | ARE*                    |  |

| 0         | C3:5            | AWE*                    |  |

Table 1–7: Control channel group assignments (cont.)

By default Table 1–8 ByteEnbl channel group assignments are not displayed.

Table 1–8: ByteEnbl channel group assignments

| Bit order | Section:channel | C6201/C6701 signal name |  |

|-----------|-----------------|-------------------------|--|

| 3         | C1:7            | BE3*                    |  |

| 2         | C1:6            | BE2*                    |  |

| 1         | C1:5            | BE1*                    |  |

| 0         | C1:4            | BE0*                    |  |

By default Table 1–9 CESpace channel group assignments are not displayed.

Table 1–9: CESpace channel group assignments

| Bit order | Section:channel | C6201/C6701 signal name |  |

|-----------|-----------------|-------------------------|--|

| 3         | C1:3            | CE3*                    |  |

| 2         | C1:2            | CE2*                    |  |

| 1         | C1:1            | CE1*                    |  |

| 0         | C1:0            | CE0*                    |  |

By default Table 1–10 Intr channel group assignments are not displayed.

Table 1–10: Intr channel group assignments

| Bit order | Section:channel | C6201/C6701 signal name |  |

|-----------|-----------------|-------------------------|--|

| 5         | C0:0            | IACK                    |  |

| 4         | C0:1            | NMI                     |  |

| 3         | C0:2            | INUM0                   |  |

| 2         | C0:3            | INUM1                   |  |

| Bit order | Section:channel | C6201/C6701 signal name |  |

|-----------|-----------------|-------------------------|--|

| 1         | C0:4            | INUM2                   |  |

| 0         | C0:5            | INUM3                   |  |

Table 1–10: Intr channel group assignments (cont.)

By default Table 1–11 Misc channel group assignments are not displayed.

Table 1–11: Misc channel group assignments

| Bit order | Section:channel | C6201/C6701 signal name |  |

|-----------|-----------------|-------------------------|--|

| 5         | C2:4            | CLKOUT1                 |  |

| 4         | C3:7            | CLKOUT2                 |  |

| 3         | C2:7            | SDA10                   |  |

| 2         | C3:6            | ARDY                    |  |

| 1         | C3:4            | AOE*                    |  |

| 0         | C0:7            | HOLD*                   |  |

Table 1–12 lists the probe section and clock and qualifier channel assignments. The clock probes are not part of any group.

| Section:channel | C6201/C6701 signal name |

|-----------------|-------------------------|

| CLK:0           | ARE*=                   |

| CLK:1           | SSCLK                   |

| CLK:2           | SDCLK                   |

| CLK:3           | CLKOUT1=                |

| C2:0            | SDRAS*                  |

| C2:1            | SDCAS*                  |

| C2:2            | SSWE*                   |

| C2:3            | AWE*=                   |

| QUAL:0          | SSADS*=                 |

| QUAL:1          | SDWE*=                  |

Table 1–12: Clock and Qualifier channel assignments

Table 1–13 lists the C6201/C6701 signals not required by the Clocking State Machine (CSM) or disassembler. The C6201/C6701 signals can be removed from their default connections and reattached to other signals of interest.

| Signal name                   | Section:channel |

|-------------------------------|-----------------|

| IACK,NMI,INUM0–3 <sup>1</sup> | C0:0 – 5        |

| CLKOUT1 <sup>1</sup>          | C2:4            |

| CLKOUT2 <sup>2</sup>          | C3:7            |

| SDA10 <sup>2</sup>            | C2:7            |

| ARDY <sup>2</sup>             | C3:6            |

| AOE*2                         | C3:4            |

| HOLD*2                        | C0:7            |

Table 1–13: Signals not required for clocking and disassembly

<sup>1</sup> Intr group <sup>2</sup> Misc group

Acquisition Setup. The TMS 710 TMS320C6201/C6701support affects the logic analyzer setup menus (and submenus) by modifying existing fields and adding micro-specific fields.

The TMS 710 TMS320C6201/C6701 support adds the selection C62XX to the Load Support Package dialog box, under the File pulldown menu. Once the C62XX support has been loaded, the Custom clocking mode selection in the module Setup menu is also enabled.

#### **CPU To Mictor Connections**

To probe the microprocessor you will need to make connections between the CPU and the Mictor pins of the P6434 Mass Termination Probe. Refer to the *P6434 Mass Termination Probe* manual, Tektronix part number 070-9793-xx, for more information on mechanical specifications. Tables 1–14 through 1–16 list the CPU pin to Mictor pin connections.

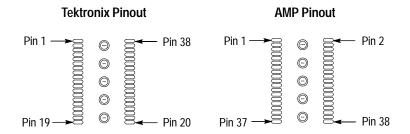

Tektronix uses a counterclockwise pin assignment. Pin-1 is located at the top left, and pin-2 is located directly below it. Pin-20 is located on the bottom right, and pin-21 is located directly above it.

AMP uses an odd side-even side pin assignment. Pin-1 is located at the top left, and pin-3 is located directly below it. Pin-2 is located on the top right, and pin-4 is located directly below it (see Figure 1-1).

**NOTE**. When designing Mictor connectors into your system under test, always follow the Tektronix pin assignment.

#### Figure 1–1: Pin assignments for a Mictor connector (component side)

**NOTE**. To protect the CPU and the inputs of the module, it is recommended that a 180  $\Omega$  resistor is connected in series between each ball pad of the CPU and each pin of the Mictor connector. The resistor must be within 1/2 inch of the ball pad of the CPU.

| Tektronix<br>Mictor A<br>pin number | AMP<br>Mictor A<br>pin number | Logic analyzer<br>channel | C6201/C6701<br>signal name | Pin number |

|-------------------------------------|-------------------------------|---------------------------|----------------------------|------------|

| 1                                   | 1                             | NC                        | NC                         | NC         |

| 2                                   | 3                             | NC                        | NC                         | NC         |

| 3                                   | 5                             | CLOCK:0                   | ARE*=                      | Y24        |

| 4                                   | 7                             | A3:7                      | GND                        | GND        |

| 5                                   | 9                             | A3:6                      | GND                        | GND        |

| 6                                   | 11                            | A3:5                      | GND                        | GND        |

| 7                                   | 13                            | A3:4                      | GND                        | GND        |

| 8                                   | 15                            | A3:3                      | GND                        | GND        |

| 9                                   | 17                            | A3:2                      | GND                        | GND        |

| 10                                  | 19                            | A3:1                      | GND                        | GND        |

| 11                                  | 21                            | A3:0                      | GND                        | GND        |

| 12                                  | 23                            | A2:7                      | GND                        | GND        |

| 13                                  | 25                            | A2:6                      | GND                        | GND        |

| 14                                  | 27                            | A2:5                      | EA21                       | J26        |

| 15                                  | 29                            | A2:4                      | EA20                       | K25        |

| 16                                  | 31                            | A2:3                      | EA19                       | L24        |

#### Table 1–14: CPU to Mictor connections for Mictor A pins

| Tektronix<br>Mictor A<br>pin number | AMP<br>Mictor A<br>pin number | Logic analyzer<br>channel | C6201/C6701<br>signal name | Pin number |

|-------------------------------------|-------------------------------|---------------------------|----------------------------|------------|

| 17                                  | 33                            | A2:2                      | EA18                       | K26        |

| 18                                  | 35                            | A2:1                      | EA17                       | M26        |

| 19                                  | 37                            | A2:0                      | EA16                       | M25        |

| 20                                  | 38                            | A0:0                      | GND                        | GND        |

| 21                                  | 36                            | A0:1                      | GND                        | GND        |

| 22                                  | 34                            | A0:2                      | EA2                        | Y26        |

| 23                                  | 32                            | A0:3                      | EA3                        | W25        |

| 24                                  | 30                            | A0:4                      | EA4                        | V24        |

| 25                                  | 28                            | A0:5                      | EA5                        | W26        |

| 26                                  | 26                            | A0:6                      | EA6                        | V25        |

| 27                                  | 24                            | A0:7                      | EA7                        | V26        |

| 28                                  | 22                            | A1:0                      | EA8                        | T23        |

| 29                                  | 20                            | A1:1                      | EA9                        | U25        |

| 30                                  | 18                            | A1:2                      | EA10                       | U26        |

| 31                                  | 16                            | A1:3                      | EA11                       | R23        |

| 32                                  | 14                            | A1:4                      | EA12                       | T26        |

| 33                                  | 12                            | A1:5                      | EA13                       | R25        |

| 34                                  | 10                            | A1:6                      | EA14                       | P24        |

| 35                                  | 8                             | A1:7                      | EA15                       | P25        |

| 36                                  | 6                             | CLOCK:1                   | SSCLK                      | AD17       |

| 37                                  | 4                             | NC                        | NC                         | NC         |

| 38                                  | 2                             | NC                        | NC                         | NC         |

| 39                                  | 39                            | GND                       | GND                        | GND        |

| 40                                  | 40                            | GND                       | GND                        | GND        |

| 41                                  | 41                            | GND                       | GND                        | GND        |

| 42                                  | 42                            | GND                       | GND                        | GND        |

| 43                                  | 43                            | GND                       | GND                        | GND        |

| 44                                  | 44                            | GND                       | GND                        | GND        |

Table 1-14: CPU to Mictor connections for Mictor A pins (cont.)

| Tektronix<br>Mictor D<br>pin number | AMP<br>Mictor D<br>pin number | LA channel | C6201/C6701<br>signal name | Pin number |

|-------------------------------------|-------------------------------|------------|----------------------------|------------|

| 1                                   | 1                             | NC         | NC                         | NC         |

| 2                                   | 3                             | NC         | NC                         | NC         |

| 3                                   | 5                             | Qual:0     | SSADS*=                    | AC20       |

| 4                                   | 7                             | D3:7       | ED31                       | AB2        |

| 5                                   | 9                             | D3:6       | ED30                       | AC1        |

| 6                                   | 11                            | D3:5       | ED29                       | AA4        |

| 7                                   | 13                            | D3:4       | ED28                       | AD1        |

| 8                                   | 15                            | D3:3       | ED27                       | AC3        |

| 9                                   | 17                            | D3:2       | ED26                       | AD4        |

| 10                                  | 19                            | D3:1       | ED25                       | AF3        |

| 11                                  | 21                            | D3:0       | ED24                       | AE4        |

| 12                                  | 23                            | D2:7       | ED23                       | AD5        |

| 13                                  | 25                            | D2:6       | ED22                       | AF4        |

| 14                                  | 27                            | D2:5       | ED21                       | AE5        |

| 15                                  | 29                            | D2:4       | ED20                       | AD6        |

| 16                                  | 31                            | D2:3       | ED19                       | AE6        |

| 17                                  | 33                            | D2:2       | ED18                       | AD7        |

| 18                                  | 35                            | D2:1       | ED17                       | AC8        |

| 19                                  | 37                            | D2:0       | ED16                       | AF7        |

| 20                                  | 38                            | D0:0       | ED0                        | AC17       |

| 21                                  | 36                            | D0:1       | ED1                        | AF19       |

| 22                                  | 34                            | D0:2       | ED2                        | AF18       |

| 23                                  | 32                            | D0:3       | ED3                        | AE17       |

| 24                                  | 30                            | D0:4       | ED4                        | AC15       |

| 25                                  | 28                            | D0:5       | ED5                        | AF16       |

| 26                                  | 26                            | D0:6       | ED6                        | AE15       |

| 27                                  | 24                            | D0:7       | ED7                        | AF15       |

| 28                                  | 22                            | D1:0       | ED8                        | AE14       |

| 29                                  | 20                            | D1:1       | ED9                        | AF11       |

| 30                                  | 18                            | D1:2       | ED10                       | AE11       |

| 31                                  | 16                            | D1:3       | ED11                       | AE10       |

| 32                                  | 14                            | D1:4       | ED12                       | AC11       |

| 33                                  | 12                            | D1:5       | ED13                       | AF9        |

| 34                                  | 10                            | D1:6       | ED14                       | AD10       |

| 35                                  | 8                             | D1:7       | ED15                       | AD9        |

Table 1–15: CPU to Mictor connections for Mictor D pins

| Tektronix<br>Mictor D<br>pin number | AMP<br>Mictor D<br>pin number | LA channel | C6201/C6701<br>signal name | Pin number |

|-------------------------------------|-------------------------------|------------|----------------------------|------------|

| 36                                  | 6                             | CLOCK:2    | SDCLK                      | AE20       |

| 37                                  | 4                             | NC         | NC                         | NC         |

| 38                                  | 2                             | NC         | NC                         | NC         |

| 39                                  | 39                            | GND        | GND                        | GND        |

| 40                                  | 40                            | GND        | GND                        | GND        |

| 41                                  | 41                            | GND        | GND                        | GND        |

| 42                                  | 42                            | GND        | GND                        | GND        |

| 43                                  | 43                            | GND        | GND                        | GND        |

| 44                                  | 44                            | GND        | GND                        | GND        |

Table 1–15: CPU to Mictor connections for Mictor D pins (cont.)

Table 1–16: CPU to Mictor connections for Mictor C pins

| Tektronix-<br>Mictor C<br>pin number | AMP<br>Mictor C<br>pin number | LA channel | C6201/C6701<br>signal name | Pin number |

|--------------------------------------|-------------------------------|------------|----------------------------|------------|

| 1                                    | 1                             | NC         | NC                         | NC         |

| 2                                    | 3                             | NC         | NC                         | NC         |

| 3                                    | 5                             | CLOCK:3    | CLKOUT1=                   | AF22       |

| 4                                    | 7                             | C3:7       | CLKOUT2                    | AF20       |

| 5                                    | 9                             | C3:6       | ARDY                       | W23        |

| 6                                    | 11                            | C3:5       | AWE*                       | AD23       |

| 7                                    | 13                            | C3:4       | AOE*                       | AC24       |

| 8                                    | 15                            | C3:3       | ARE*                       | Y24        |

| 9                                    | 17                            | C3:2       | LENDIAN                    | H3         |

| 10                                   | 19                            | C3:1       | RESET*                     | K2         |

| 11                                   | 21                            | C3:0       | SDWE*                      | AF23       |

| 12                                   | 23                            | C2:7       | SDA10                      | AD21       |

| 13                                   | 25                            | C2:6       | SSADS*                     | AC20       |

| 14                                   | 27                            | C2:5       | SSOE*                      | AF21       |

| 15                                   | 29                            | C2:4       | CLKOUT1                    | AF22       |

| 16                                   | 31                            | C2:3       | AWE*=                      | AD23       |

| 17                                   | 33                            | C2:2       | SSWE*                      | AD19       |

| 18                                   | 35                            | C2:1       | SDCAS*                     | AD22       |

| 19                                   | 37                            | C2:0       | SDRAS*                     | AF24       |

| 20                                   | 38                            | C0:0       | IACK                       | Y2         |

| Tektronix-<br>Mictor C<br>pin number | AMP<br>Mictor C<br>pin number | LA channel | C6201/C6701<br>signal name | Pin number |

|--------------------------------------|-------------------------------|------------|----------------------------|------------|

| 21                                   | 36                            | C0:1       | NMI                        | L2         |

| 22                                   | 34                            | C0:2       | INUMO                      | AB1        |

| 23                                   | 32                            | C0:3       | INUM1                      | AA2        |

| 24                                   | 30                            | C0:4       | INUM2                      | W4         |

| 25                                   | 28                            | C0:5       | INUM3                      | AA1        |

| 26                                   | 26                            | C0:6       | HOLDA*                     | A7         |

| 27                                   | 24                            | C0:7       | HOLD*                      | AA25       |

| 28                                   | 22                            | C1:0       | CE0*                       | AC26       |

| 29                                   | 20                            | C1:1       | CE1*                       | AB24       |

| 30                                   | 18                            | C1:2       | CE2*                       | AD26       |

| 31                                   | 16                            | C1:3       | CE3*                       | AE22       |

| 32                                   | 14                            | C1:4       | BE0*                       | AA26       |

| 33                                   | 12                            | C1:5       | BE1*                       | Y23        |

| 34                                   | 10                            | C1:6       | BE2*                       | AA24       |

| 35                                   | 8                             | C1:7       | BE3*                       | AB25       |

| 36                                   | 6                             | Qual:1     | SDWE*=                     | AF23       |

| 37                                   | 4                             | NC         | NC                         | NC         |

| 38                                   | 2                             | NC         | NC                         | NC         |

| 39                                   | 39                            | GND        | GND                        | GND        |

| 40                                   | 40                            | GND        | GND                        | GND        |

| 41                                   | 41                            | GND        | GND                        | GND        |

| 42                                   | 42                            | GND        | GND                        | GND        |

| 43                                   | 44                            | GND        | GND                        | GND        |

| 44                                   | 44                            | GND        | GND                        | GND        |

Table 1–16: CPU to Mictor connections for Mictor C pins (cont.)

Getting Started

# **Operating Basics**

## Setting Up the Support

The information in this section is specific to the operations and functions of the TMS 710 TMS320C6201/C6701 microprocessor support on any Tektronix logic analyzer for which it can be purchased.

Before you acquire and display disassembled data, you need to load the support and specify setups for clocking and triggering as described in the information on basic operations. The microprocessor support provides default values for each of these setups as well as user-definable settings.

#### **Channel Group Definitions**

The software automatically defines channel groups for the support. The channel groups for the TMS 710 TMS320C6201/C6701 support are Address, Data, Control, AsyncCtrl, SbsramCtrl, SdramCtrl, ByteEnbl, CESpace, Intr, and Misc.

### Clocking

| Options         | The TMS 710 TMS320C6201/C6701support offers a microprocessor-specific clocking mode for the C6201/C6701 microprocessor. This clocking mode is the default selection whenever you load the TMS 710 TMS320C6201/C6701 support. |                                                                                                                                                                                  |           |  |  |

|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|--|--|

|                 | Disassembly will not be correct with the Internal or External clocking mo<br>Information on basic operations describes how to use these clock selection<br>general purpose analysis.                                         |                                                                                                                                                                                  |           |  |  |

| Custom Clocking | <b>Stom Clocking</b> When Custom is selected, the Custom Clocking Options menu v<br>subtitle C6201/C6701 Microprocessor Clocking Support added,<br>options will also be displayed.                                           |                                                                                                                                                                                  |           |  |  |

|                 | (CSM). There i                                                                                                                                                                                                               | D TMS320C6201/C6701support has three clock state machines<br>e is one select field with the label Memory Type: that field will<br>ollowing selections: ASYNC, SBSRAM, and SDRAM. |           |  |  |

|                 | Memory operation type:                                                                                                                                                                                                       |                                                                                                                                                                                  |           |  |  |

|                 | ASYNC<br>SBSRAM<br>SDRAM                                                                                                                                                                                                     | Selects CSM for ASYNC<br>Selects CSM for SBSRAM<br>Selects CSM for SDRAM                                                                                                         | (default) |  |  |

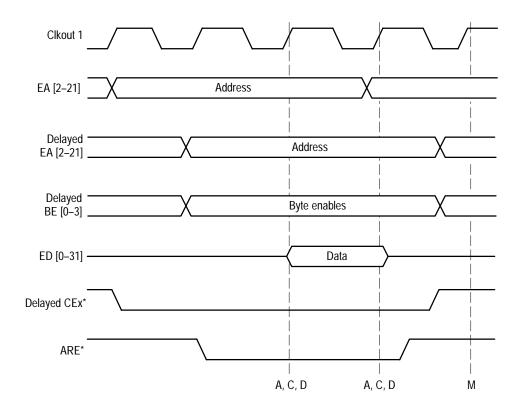

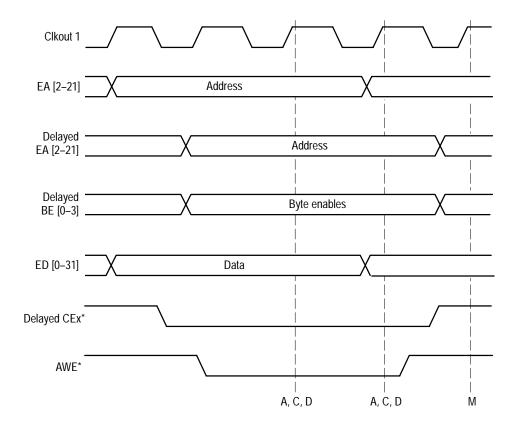

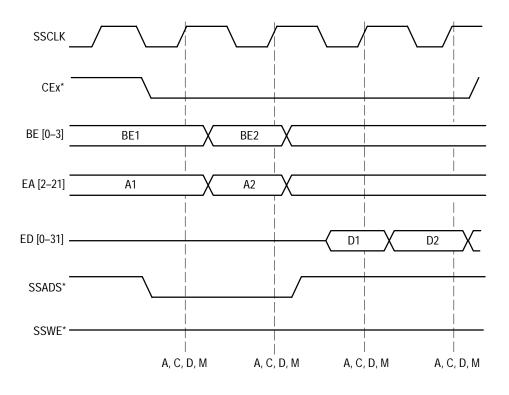

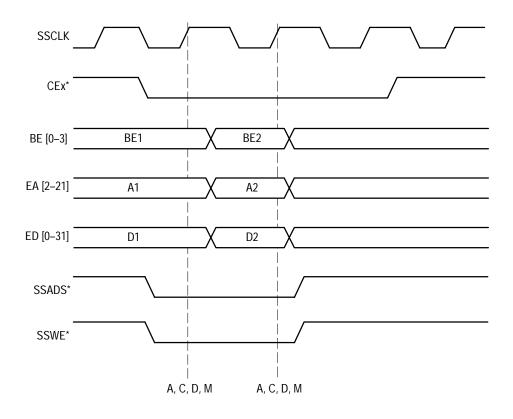

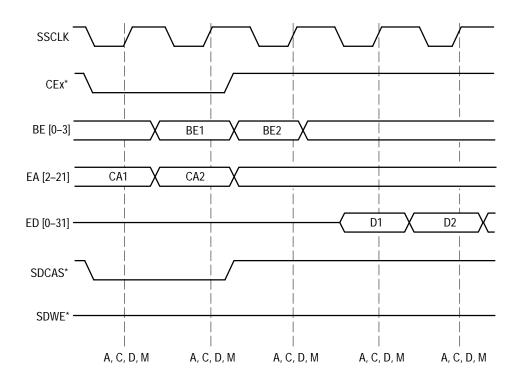

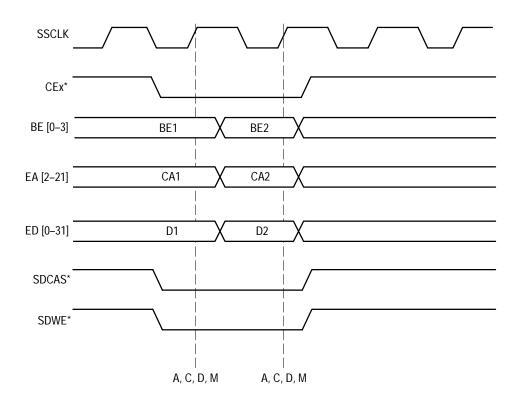

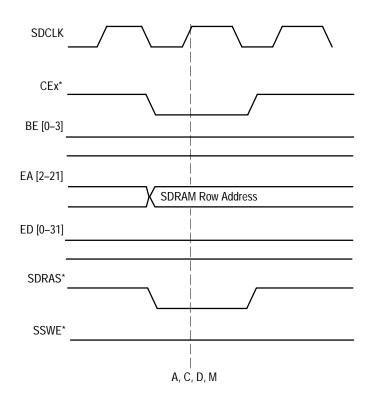

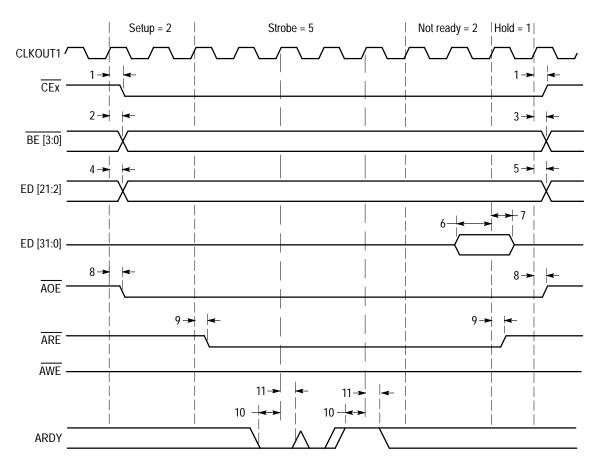

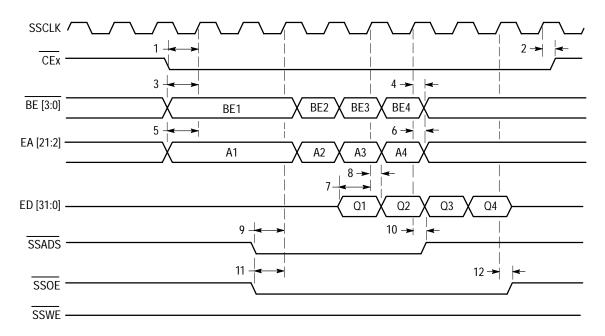

Figures 2–1 through 2–7 illustrate the bus timing for the ASYNC, SBSRAM and SDRAM memory operations.

Figure 2–1: Bus timing for the ASYNC Memory Read operation

Figure 2–2: Bus timing for the ASYNC Memory Write operation

Figure 2-3: Bus timing for the SBSRAM Memory Read operation

Figure 2–4: Bus timing for the SBSRAM Memory Write operation

Figure 2-5: Bus timing for the SDRAM Memory Read operation

Figure 2–6: Bus timing for the SDRAM Memory Write operation

Figure 2–7: Bus timing for the SDRAM row address activation cycle

#### **Symbols**

The TMS 710 TMS320C6201/C6701support supplies one symbol table file. The C6201/C6701\_Ctrl file replaces specific Control channel group values with symbolic values when Symbolic is the radix for the channel group.

Symbol tables are generally not for use in timing or C6201/C6701\_T support disassembly.

Table 2–1 lists the name, bit pattern, and description for the symbols in the C6201/C6701\_Ctrl, in the Control channel group symbol table.

|                          | Control group value                                                             |                                 |

|--------------------------|---------------------------------------------------------------------------------|---------------------------------|

| Symbol                   | RESET* SDCAS* SSWE*<br>LENDIAN SDWE* ARE*<br>HOLDA* SSADS* AWE*<br>SDRAS* SSOE* | Description                     |

| RESET                    | 0 X X X X X X X X X X X                                                         | Processor in Reset              |

| Alt Master<br>Cycle      | 1 X O X X X X X X X X                                                           | Alternate Bus Master cycle      |

| SDRAM Row<br>Addr        | 1 X 1 0 1 1 1 1 1 1 1                                                           | SDRAM Row Address cycle         |

| SDRAM Write              | 1 X 1 1 0 0 1 1 1 1 1                                                           | Write cycle to SDRAM            |

| SDRAM Read               | 1 X 1 1 0 1 1 1 1 1 1                                                           | Read cycle to SDRAM             |

| SDRAM MRS                | 1 X 1 0 0 0 1 1 1 1 1                                                           | Sets the mode register of SDRAM |

| SBSRAM<br>Read           | 1 X 1 X X X 0 0 1 1 1                                                           | Read cycle to SBSRAM            |

| SDRAM/<br>SBSRAM<br>Read | 1 X 1 X X X X X X 1 1 1                                                         | Read cycle to SDRAM or SBSRAM   |

| SBSRAM<br>Write          | 1 X 1 X X X 0 1 0 1 1                                                           | Write cycle to SBSRAM           |

| ASYNC Read               | 1 X 1 X X X 1 1 1 0 1                                                           | Read cycle to ASYNC             |

| ASYNC Write              | 1 X 1 X X X 1 1 1 1 0                                                           | Write cycle to ASYNC            |

#### Table 2–1: Control group symbol table definitions

#### Logic Analyzer Time Alignment for the C6201

The setup time alignment of the logic analyzer to a system under test may be necessary if the C6201 microprocessor operates at a frequency greater than listed in Table 2–2 with similar memory types. To ensure that the logic analyzer acquires correct data at higher clock speeds, you may need to follow these procedures and make the setup timing adjustments.

| Memory type  | TMS 710 C6201 supported<br>maximum frequencies<br>without alignment | C6201 maximum |

|--------------|---------------------------------------------------------------------|---------------|

| Asynchronous | 115 MHz                                                             | 200 MHz       |

| SBSRAM       | 180 MHz                                                             | 200 MHz       |

| SDRAM        | 200 MHz                                                             | 200 MHz       |

Table 2-2: C6201 Memory types and maximum frequencies

For the Asynchronous and SBSRAM memories, the supported maximum frequency can be increased by following step 1 through step 18. A setup time alignment procedure is not included for the SDRAM memory, since the memory operates at the supported maximum frequency.

- 1. From the System window in the File menu, select Load System.

- 2. From the Load System dialog box, browse to where the Cal\_Setup.tla file is located. Figure 2–8 shows the Load System window with the Cal\_Setup.tla system setups.

| Load System                                  |                                |          | ?                      | х |

|----------------------------------------------|--------------------------------|----------|------------------------|---|

| Look jn:                                     | 🔄 C62xx                        | • E      |                        |   |

| บาใC62≫.tla<br>บาใCal_Setup<br>บาใDemo.tla   |                                |          |                        |   |

| File <u>n</u> ame:<br>Files of <u>t</u> ype: | Cal_Setup.tla<br>TLA 700 Files | <u>_</u> | <u>O</u> pen<br>Cancel |   |

Figure 2–8: C6201 Setup: Load System menu

**3.** Select the Cal\_Setup.tla file and click open. Click No in the caution dialog box. If an Information dialog box appears, click OK.

The Load System Options dialog box may or may not appear.

**4.** If the Load System Options dialog box appears and the C62XX setup is not loaded to the Current System, then drag the C62XX icon to the desired module and click OK. If an information box appears click OK.

Figure 2–9 shows the Load System Options dialog box before dragging the C6201 icon to the module in the Current System.

| Lo | ad System Options                                                                                                                                             | X            |

|----|---------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

|    | Drag modules in the saved system onto desired modules in the current system. Reference data sources and data windows in the saved system will also be loaded. |              |

|    | Cal_Setup                                                                                                                                                     | ार्थ के<br>- |

|    | <u></u>                                                                                                                                                       |              |

|    | Current System                                                                                                                                                |              |

|    |                                                                                                                                                               |              |

|    | Cancel Help                                                                                                                                                   |              |

Figure 2–9: C6201 Load System Options dialog box

| 📰 System                |           |            |

|-------------------------|-----------|------------|

| Logic _F보ూਓ<br>Analyzer |           |            |

| On □ □ □ □ □ □          |           |            |

|                         |           |            |

|                         |           |            |

| C62XX Cal               | Listing 1 | Waveform 1 |

Figure 2–10 shows the Cal\_Setup file loaded in the System window.

Figure 2–10: C6201 System window with the C6201 Cal Setup file

NOTE. For only SBSRAM memory calibration, go to step 10.

5. To enter the setup time values from the Setup: C62XX dialog box click the More button to the right of the Custom Clocking field. A Custom Options C62XX dialog box appears (see Figure 2–11). Select ASYNC in the Memory Type field. The logic analyzer must trigger on the falling edge of ARE\*.

| stom Option<br>62XX uP Clo | ns C62XX              | ? ×                      |

|----------------------------|-----------------------|--------------------------|

|                            | Memory Type           | ASYNC                    |

| Group                      | Setup Time            | Group Control Setup/Hold |

| Address                    | Support Package Defau | Sample Clk               |

| Data                       | Support Package Defau |                          |

| AsyncCtrl                  | Os                    |                          |

| SbsramCtrl                 | 1ns                   | ]                        |

| SdramCtrl                  | Support Package Defau |                          |

|                            |                       |                          |

|                            | ОК                    | Help                     |

Figure 2–11: C6201 Custom options C6201 dialog box

**6.** Click the Trigger icon in the System window. The Trigger: C62XX dialog box appears with a predefined trigger. Figure 2–12 shows the setup to trigger.

| 📴 Trigger: C62XX           |                                                     |                      |

|----------------------------|-----------------------------------------------------|----------------------|

| D-J L-J State Then & B B   | Storage 📶 🔽 Trigger Pos                             | <u></u> <u>50%</u> ÷ |

| Overview<br>Run<br>State 1 | State 1<br>If Channel ARE* Goes Low<br>Then Trigger |                      |

#### Figure 2–12: C6201 Trigger setup for any asynchronous memory Read

7. With the system under test running, click the RUN button to acquire data. After triggering, select the C6201 Cal Waveform Window.

# ASYNC Memory Calibration 8. In Figure 2–13 the value of the timing parameter 9 is calculated from the C6201 Cal Waveform Window for signals ARE\*= and ARE\* for both the rising and falling edge. Parameter 9 is the Delay time from CLKOUT1 high to a valid signal. The maximum (T<sub>9</sub>MAX) of the four calculated values is taken to determine the setup value of the AsyncCtrl group as described in Table 2–3. This procedure is useable if the difference between the maximum

and minimum calculated values are 2.5 ns or less.

Data supplied by Texas Instruments, Inc.

#### Figure 2–13: C6201 Asynchronous memory read timing diagram

NOTE. For only asynchronous memory calibration, go to step 15.

**9.** In the Custom Options window, click on the setup time submenu of the AsyncCtrl group. Select the setup time for the AsyncCtrl group as listed in Table 2–3 from the calculated value of parameter 9 in Figure 2–13.

| Т9МАХ                        | Setup time used for AsyncCtrl group |  |

|------------------------------|-------------------------------------|--|

| $> -1.0$ ns and $\le 1.5$ ns | Support package Default             |  |

| > 1.5 ns                     | (5 – T <sub>9</sub> MAX) ns         |  |

Table 2–3: C6201 Setup time for the AsyncCtrl group

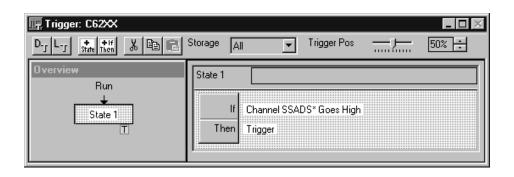

- 10. Click the Setup icon in the System window. To enter the setup time values from the Setup: C6201 dialog box, click the More button to the right of the Custom Clocking field. A Custom Options C6201 dialog box appears. In Custom Option for SBSRAM memory calibration, select SBSRAM in the memory type field. The logic analyzer must trigger on the raising edge of SSADS\*.

- **11.** Click the Trigger icon in the System window. The Trigger: C62XX dialog box appears with a predefined trigger. Figure 2–14 shows the setup to trigger.

| 📻 Trigger: C62XX           |         |           |               |         | _ 🗆 × |

|----------------------------|---------|-----------|---------------|---------|-------|

| D-J L-J State +If X B C    | Storage | All       | Trigger Pos   | <u></u> | 50% ÷ |

| Overview<br>Run<br>State 1 | The     | n Trigger | DS* Goes High |         |       |

#### Figure 2–14: C6201 Trigger setup for any SBSRAM memory Read

**12.** With the system under test running, click the RUN button to acquire data. After triggering, select the C62XX Cal Waveform Window.

SBSRAM Memory Calibration

13. In Figure 2–15 the value of timing parameter 10 is calculated from the C6201 Cal Waveform Window for signals SSADS\* and SSADS\*=. Both values should fall within the range of this timing alignment procedure to be useable. The Timing parameter 10 is the Output hold time for the signal that is valid after SSCLK high.

Data supplied by Texas Instruments, Inc.

#### Figure 2–15: C6201 SBSRAM memory read timing (full-rate SSCLK) diagram

14. In the Custom Options window click on the setup time submenu of the SbsramCtrl group. Select the setup time for the SbsramCtrl group as listed in Table 2–4 from the calculated value of parameter 10 in Figure 2–15.

| Table 2-4: C6201 | Setup time | for the SbsramCtrl | group |

|------------------|------------|--------------------|-------|

|------------------|------------|--------------------|-------|

| If the value of parameter 10 is: | Setup time used for SbsramCtrl group |  |

|----------------------------------|--------------------------------------|--|